## Help Volume

© 1992-2002 Agilent Technologies. All rights reserved.

Agilent Technologies 16717A Logic Analyzer

### Agilent Technologies 16717A Logic Analyzer

The Agilent Technologies 16717A 333 MHz State/2 GHz Timing Zoom logic analyzer offers 2M deep memory and very fast sample rates - up to 2 GHz for areas around the trigger - with up to 340 channels.

## "Getting Started" on page 11

- "Step 1. Connect the logic analyzer to the device under test" on page 13

- "Step 2. Choose the sampling mode" on page 14

- "Step 3. Format labels for the probed signals" on page 17

- "Step 4. Define the trigger condition" on page 20

- "Step 5. Run the measurement" on page 21

- "Step 6. Display the captured data" on page 22

#### "Task Guide" on page 31

- "Probing the Device Under Test" on page 33

- "Choosing the Sampling Mode" on page 36

- "Selecting the Timing Mode (Asynchronous Sampling)" on page 36

- "Selecting the State Mode (Synchronous Sampling)" on page 43

- "In Either Timing Mode or State Mode" on page 52

- "Using 2 GHz Timing Zoom" on page 54

- "Formatting Labels for Logic Analyzer Probes" on page 57

- "Setting Up Triggers and Running Measurements" on page 64

- "Using Trigger Functions" on page 65

- "Using State Mode Trigger Features" on page 70

- "Editing the Trigger Sequence" on page 72

- "Editing Advanced Trigger Functions" on page 78

- "Saving/Recalling Trigger Setups" on page 85

- "Running Measurements" on page 86

- "Displaying Captured Data" on page 88

- "Using Symbols" on page 95

- "Printing/Exporting Captured Data" on page 104

- "Solving Logic Analysis Problems" on page 108

- "Saving and Loading Logic Analyzer Configurations" on page 110

## "Reference" on page 113

- "The Sampling Tab" on page 115

- "The Format Tab" on page 119

- "The Trigger Tab" on page 146

- "The Symbols Tab" on page 159

- "Error Messages" on page 170

- "Specifications and Characteristics" on page 186

## "Concepts" on page 191

- "Understanding Logic Analyzer Triggering" on page 192

- "Understanding State Mode Sampling Positions" on page 208

#### See Also

Main System Help (see the *Agilent Technologies 16700A/B-Series Logic Analysis System* help volume)

Glossary (see page 211)

Agilent Technologies 16717A Logic Analyzer

#### Agilent Technologies 16717A Logic Analyzer

#### 1 Getting Started

- Step 1. Connect the logic analyzer to the device under test 13

- Step 2. Choose the sampling mode 14

- Step 3. Format labels for the probed signals 17

- Step 4. Define the trigger condition 20

- Step 5. Run the measurement 21

- Step 6. Display the captured data 22

- For More Information... 24

- Example: Timing measurement on counter board 26

- Example: State measurement on counter board  $\,\,\,\,28$

#### 2 Task Guide

Probing the Device Under Test 33

Choosing the Sampling Mode 36 Selecting the Timing Mode (Asynchronous Sampling) 36

| To select transitional timing or store qualified 37 More on Store Qualification in Transitional Timing 38 More on Storing Transitions 38 Transitional Timing Considerations 39 Selecting the State Mode (Synchronous Sampling) 43 In Either Timing Mode or State Mode 52 Using 2 GHz Timing Zoom 54                                   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Formatting Labels for Logic Analyzer Probes 57  To assign pods to one or two analyzers 57  To set pod threshold voltages 58  To assign probe channels to labels 59  To change the label polarity 61  To reorder bits in a label 61  To turn labels off or on 62                                                                       |

| Setting Up Triggers and Running Measurements 64 Using Trigger Functions 65 Using State Mode Trigger Features 70 Editing the Trigger Sequence 72 Editing Advanced Trigger Functions 78 Saving/Recalling Trigger Setups 85 Running Measurements 86                                                                                      |

| Displaying Captured Data 88  To open Waveform or Listing displays 88  To display Timing Zoom data 89  To use other display tools 90  If the captured data doesn't look correct 92  If there are filtered data holes in display memory 92  To display symbols for data values 93  To cancel the display processing of captured data 94 |

Using Symbols 95

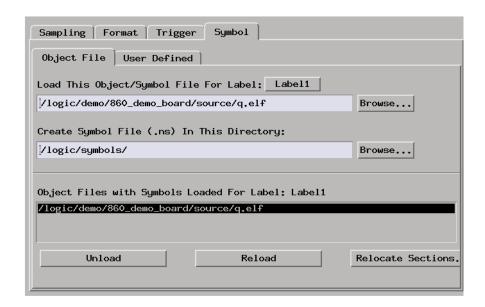

To load object file symbols 96

To adjust symbol values for relocated code 97

To create user-defined symbols 98

To enter symbolic label values 99

To create an ASCII symbol file 100

To create a readers.ini file 101

Printing/Exporting Captured Data 104

Cross-Triggering 106

To cross-trigger between two analyzers 106

To cross-trigger with another instrument 107

Solving Logic Analysis Problems 108 To test the logic analyzer hardware 108

Saving and Loading Logic Analyzer Configurations 110

#### 3 Reference

The Sampling Tab 115 Timing Mode 116 State Mode 117

The Format Tab 119

Importing Netlist and ASCII Files 121

Exporting ASCII Files 123

Importing ASCII Files 123

Termination Adapter 125

E5346A High Density Adapter 126

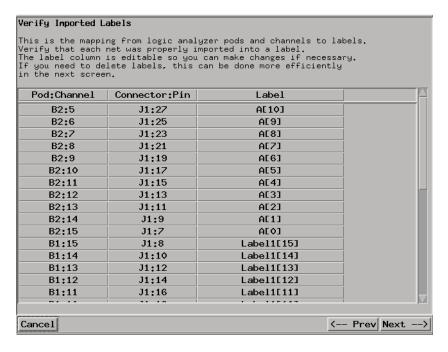

Mapping Connector Names 127

Import the Net List File 127

Verify Net to Label Mapping 128

Select/Create Interface Labels 129

Pod Assignment Dialog 130

Sampling Positions Dialog 131

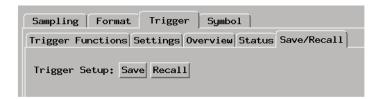

The Trigger Tab 146

Trigger Functions Subtab 147

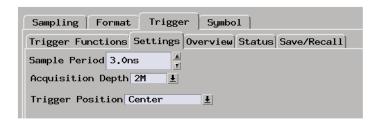

Settings Subtab 154

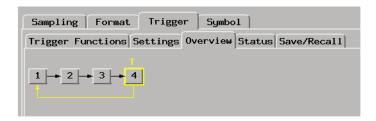

Overview Subtab 155

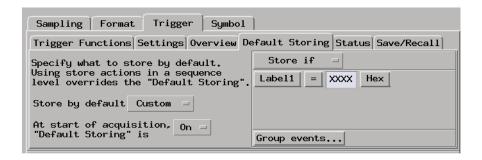

Default Storing Subtab 156

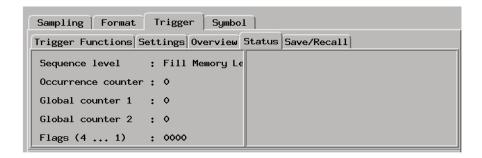

Status Subtab 157

Save/Recall Subtab 157

The Symbols Tab 159

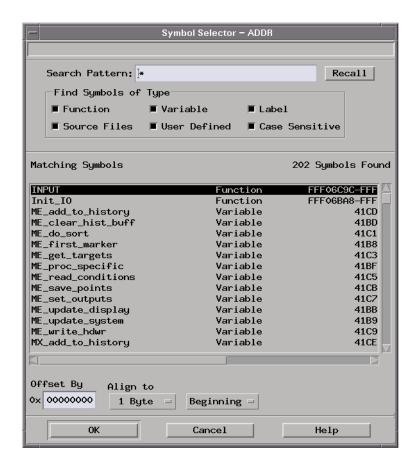

Symbols Selector Dialog 161

Symbol File Formats 163

General-Purpose ASCII (GPA) Symbol File Format 164

Error Messages 170 Must assign Pod 1 on the master card to specify actions for flags 171 Branch expression is too complex 171 Cannot specify range on label with clock bits that span pod pairs 176 Counter value checked as an event, but no increment action specified 177 Goto action specifies an undefined level 177 Maximum of 32 Channels Per Label 177 Hardware Initialization Failed 178 Must assign another pod pair to specify actions for flags 178 No more Edge/Glitch resources available for this pod pair 178 No more Pattern resources available for this pod pair 179 No Trigger action found in the trace specification 179 Slow or Missing Clock 180 Timer value checked as an event, but no start action specified 180 Trigger function initialization failure 181 Trigger inhibited during timing prestore 182 Trigger Specification is too complex 182 Waiting for Trigger 184 Analyzer armed from another module contains no "Arm in from IMB" event 185 Specifications and Characteristics 186

Agilent 16717A Logic Analyzer Specifications 186 Agilent 16717A Logic Analyzer Characteristics 186

What is a Specification? 189 What is a Characteristic? 190

#### 4 Concepts

Understanding Logic Analyzer Triggering 192

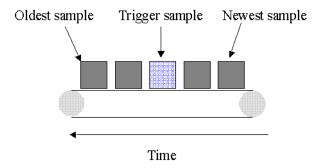

The Conveyor Belt Analogy 192

Summary of Triggering Capabilities 194

Sequence Levels 194

Boolean Expressions 197

Branches 198

Edges 198

Ranges 198

Flags 199

Occurrence Counters and Global Counters 199

Timers 200

Storage Qualification 201

Strategies for Setting Up Triggers 203

Conclusions 207

Understanding State Mode Sampling Positions 208

#### Glossary

#### Index

1

## **Getting Started**

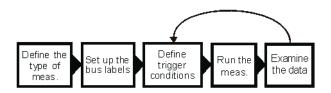

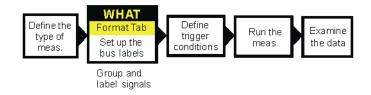

After you have connected the logic analyzer probes to your device under test (see "Step 1. Connect the logic analyzer to the device under test" on page 13), any measurement will have the following basic steps:

- "Step 2. Choose the sampling mode" on page 14

- "Step 3. Format labels for the probed signals" on page 17

- "Step 4. Define the trigger condition" on page 20

- "Step 5. Run the measurement" on page 21

- "Step 6. Display the captured data" on page 22

If you have previously saved a logic analyzer setup to a configuration file, or if configuration files are included with an analysis probe, you can load the configuration file to set up the logic analyzer and define the trigger condition.

Once you have made a logic analyzer measurement, the measurement can be refined by repeating steps 4 - 6.

Next: "Step 1. Connect the logic analyzer to the device under test" on page 13

# Step 1. Connect the logic analyzer to the device under test

Before you begin setting up the logic analyzer for a measurement, you need to physically connect the logic analyzer to your device under test.

There are several ways to connect logic analyzer probes to the device under test:

- Using the general-purpose probes, the standard flying lead set, and grabbers to connect to pins and leads in the device under test.

- By designing connectors (headers) into the device under test so that logic analyzer probe cables and termination adapters can plug in directly.

- By designing connectors (headers) and terminations into the device under test so that logic analyzer probe cables can plug in directly.

- Using an *analysis probe* to connect to microprocessors and standard buses.

When using an analysis probe, the Setup Assistant guides you through the connection and setup process for your particular logic analyzer and analysis probe.

When connecting logic analyzer probes to the device under test:

- 1. Attach the logic analyzer probes to the device under test in a way that keeps logically-related *channels* together.

- 2. Be sure to ground each pod.

Next: "Step 2. Choose the sampling mode" on page 14

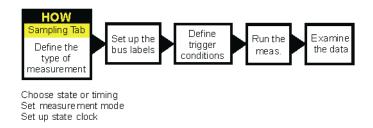

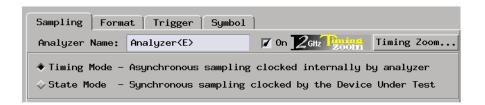

### Step 2. Choose the sampling mode

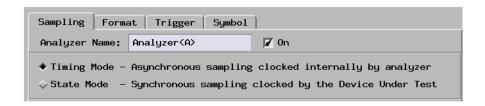

There are two logic analyzer sampling modes to choose from: *timing* mode and *state* mode.

In *timing mode*, the logic analyzer samples asynchronously, based on an internal sampling clock signal.

In *state mode*, the logic analyzer samples synchronously, based on a sampling clock signal (or signals) from the device under test. Typically, the signal used for sampling in state mode is a state machine or microprocessor clock signal.

#### To choose the sampling mode

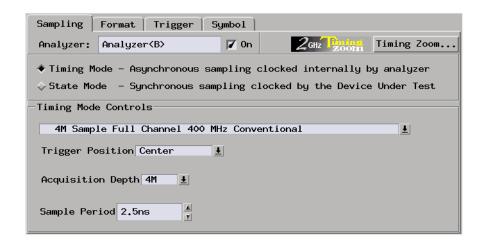

1. In the Sampling tab, choose *Timing Mode* or *State Mode*.

#### If you chose Timing Mode

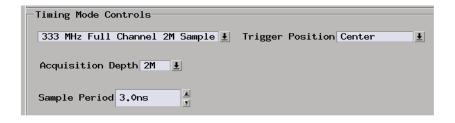

1. Select the timing analyzer full/half channel configuration.

Typically, you can choose a *half-channel* configuration with faster sampling and greater memory depth, but with half of the channels.

2. Set the sample period.

To capture signal level changes reliably, the sample period should be less than half (many engineers prefer one-fourth) of the period of the fastest signal you want to measure.

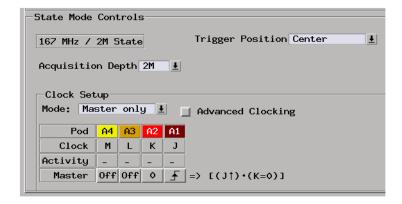

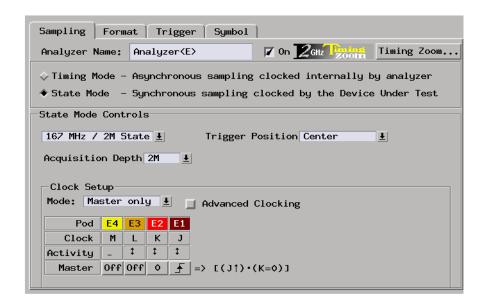

#### If you chose State Mode

- 1. Select the state analyzer speed configuration (if there is a configuration option).

- 2. In the Clock Setup, using the *Master only* mode, specify which clock signal edges from the device under test will be used as the sampling clock.

#### Step 2. Choose the sampling mode

You can also specify clock input signal levels (from the device under test) that will enable (qualify) the sampling clock.

#### In either sampling mode

1. Specify the trigger position.

The trigger is the event in the device under test that you want to capture data around.

Specify whether you want to look at data after the trigger (Start), before and after the trigger (Center), before the trigger (End), or use a percentage of the logic analyzer's memory for data after the trigger (User Defined).

2. Set the acquisition memory depth.

If you need less data and want measurements to run faster, you can limit the amount of trace memory that is filled with samples.

Next: "Step 3. Format labels for the probed signals" on page 17

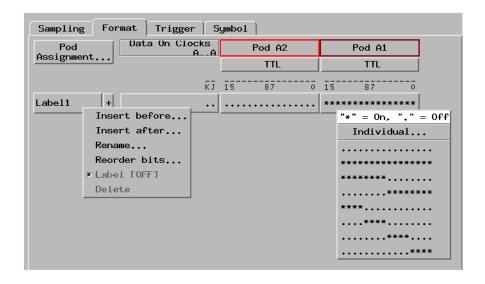

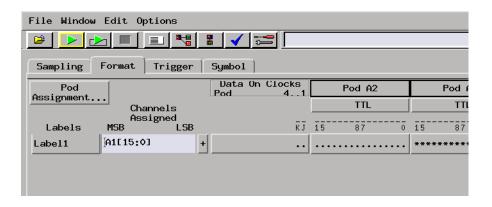

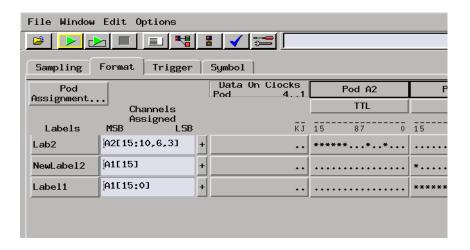

### Step 3. Format labels for the probed signals

When a logic analyzer probes hundreds of signals in a device under test, you need to be able to give those channels more meaningful names than "pod 1, channel 1".

The Format tab is mainly for assigning bus and signal names (from the device under test), to logic analyzer channels. These names are called *labels*. Labels are used when setting up triggers and displaying captured data.

The Format tab also lets you do things like assign pod pairs to one or two logic analyzers and specify the logic analyzer threshold voltage.

The Format tab has activity indicators that show whether the signal a channel is probing is above the threshold voltage (high), below the threshold voltage (low), or transitioning.

#### To assign pods to one or two logic analyzers

A logic analyzer's pod pairs can be assigned to one or two separate logic analyzers or they can be left unassigned.

- 1. In the Format tab, select the *Pod Assignment* button.

- 2. In the Pod Assignment dialog, drag a pod pair to the appropriate logic analyzer.

- 3. Select the Close button.

#### To specify threshold voltages

The *threshold voltage* is the voltage level that a signal must cross before the logic analyzer recognizes a change in logic levels.

- 1. In the Format tab, select the button under the pod name.

- 2. In the Pod threshold dialog, select the desired *Standard* or *User Defined* threshold voltage.

- 3. Select the Close button.

#### To assign names to logic analyzer channels

- 1. Select a label button, and either:

- Choose the Rename command, enter the label name, and select the OK button.

- Or, choose the *Insert before* or *Insert after* command, enter the label name, and select the OK button.

- 2. In the label row, select the button of the pod that contains the channels you want to assign.

- 3. Either choose one of the standard label assignments--dots (.) mean the channel is unassigned, asterisks (\*) mean the channel is assigned--or choose *Individual*.

If you chose Individual:

- a. In the "label pod" dialog, select the channels you want to assign/unassign.

- b. Select the OK button.

Next: "Step 4. Define the trigger condition" on page 20

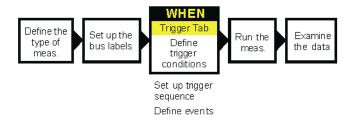

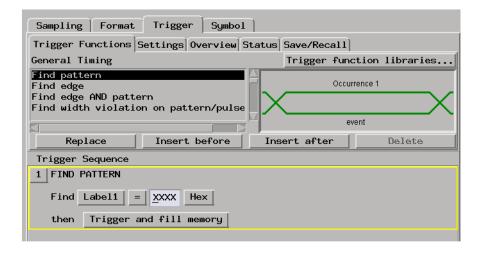

### Step 4. Define the trigger condition

The trigger is the event in the device under test that you want to capture data around.

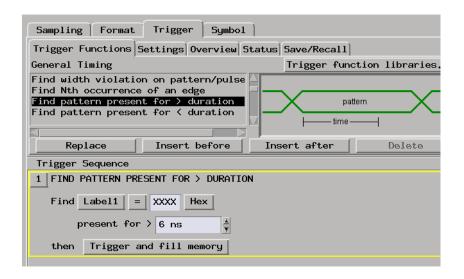

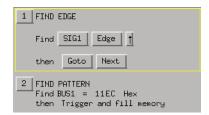

1. In the Trigger tab, and in the Trigger Functions subtab, choose the type of trigger you want to specify, and select the *Replace* button.

2. In the Trigger Sequence portion of the Trigger tab, select the buttons to define the label values and/or other conditions you want to trigger on.

Next: "Step 5. Run the measurement" on page 21

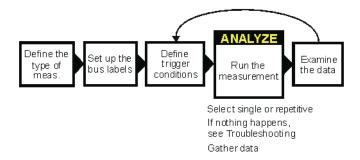

### Step 5. Run the measurement

Once the trigger condition has been defined, you can run the measurement.

1. Select the Run Single button .

condition.

Logic analyzers with deep acquisition memory take a noticeable amount of time to complete a run; however, messages like "Waiting in level 1" may indicate you need to stop the measurement and refine the trigger

When the trigger condition is found, logic analyzer acquisition memory is filled, the captured data is processed to the display tools, and the Run Single button becomes available again.

Next: "Step 6. Display the captured data" on page 22

the logic analyzer looks for the trigger condition.

### Step 6. Display the captured data

Once you have run a measurement and filled the logic analyzer's acquisition memory with captured data, you can display it with one of the display tools.

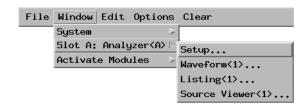

#### To open Waveform or Listing displays

Waveform displays are typically used when data is captured with the timing sampling mode, and Listing displays are used when data is captured with the state sampling mode.

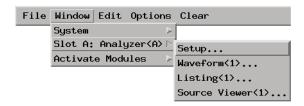

1. From the Window menu, select your logic analyzer and choose the *Waveform* or *Listing* command.

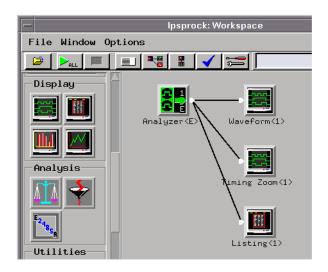

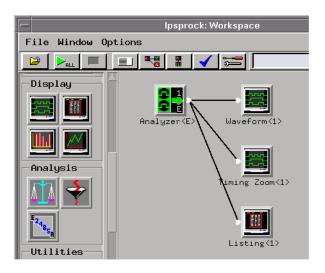

#### To add display tools via the Workspace window

- 1. Select the Workspace button (or from the Window menu, select System and Workspace).

- 2. In the Workspace window, scroll down to the Display portion of the tool icon list.

- 3. Drag the display tool icon and drop it on the analyzer icon.

- 4. To open the display tool, select its icon and choose the *Display* command.

Next: "For More Information..." on page 24

### For More Information...

# On making measurements on the demo counter board:

- "Example: Timing measurement on counter board" on page 26

- "Example: State measurement on counter board" on page 28

- *Making Basic Measurements* for a self-paced tutorial

## On connecting the logic analyzer:

- "Probing the Device Under Test" on page 33

- Setup Assistant (see the *Setup Assistant* help volume) (when using analysis probes).

- Logic Analysis System and Measurement Modules Installation Guide for probe pinout and circuit diagrams.

## On choosing the sampling mode:

- "Choosing the Sampling Mode" on page 36

- "The Sampling Tab" on page 115

## On formatting labels for probed signals:

- "Formatting Labels for Logic Analyzer Probes" on page 57

- "The Format Tab" on page 119

## On defining the trigger condition:

- "Understanding Logic Analyzer Triggering" on page 192

- "Setting Up Triggers and Running Measurements" on page 64

- "The Trigger Tab" on page 146

## On running measurements:

• "Running Measurements" on page 86

## On displaying captured data:

- "Displaying Captured Data" on page 88

- Using the Waveform Display Tool (see the *Waveform Display Tool* help volume)

- Using the Listing Display Tool (see the *Listing Display Tool* help volume)

- Working with Markers (see the *Markers* help volume)

- Using the Chart Display Tool (see the *Chart Display Tool* help volume)

- $\bullet \;\;$  Using the Distribution Display Tool (see the  $Distribution \; Display \; Tool$

help volume)

• Using the Compare Analysis Tool (see the *Compare Tool* help volume)

# Example: Timing measurement on counter board

This example uses the demo counter board that is supplied with the *Making Basic Measurements* kit as the device under test. The kit is supplied with every logic analysis system, or can be ordered from your Agilent Technologies Sales Office.

#### To connect the logic analyzer to the device under test

Connect Pod 1 of the logic analyzer to J1 on the demo counter board.

The demo counter board has built-in terminations and header connectors.

#### To choose the sampling mode

- 1. In the Sampling tab, choose *Timing Mode*.

- 2. Enter a sample period of 3.0 ns.

#### To format labels for the probed signals

- 1. In the Format tab, select the button under the pod 1.

- 2. In the Pod threshold dialog, select TTL; then, select the Close button.

- 3. Select a label button.

- 4. Choose the Rename command, enter the label name "TCOUNT", and select the OK button.

- 5. In the label row, select the button under pod 1.

- 6. Choose the "......\*\*\*\*\*\*\* standard label assignment to assign the lower 8 bits of pod 1 to the "TCOUNT" label.

#### To define the trigger condition

- 1. In the Trigger tab, and in the Trigger Functions subtab, choose the "Find edge" trigger function, and select the *Replace* button.

- 2. In the Trigger Sequence portion of the Trigger tab, select the Edge button and use the Specify Glitch/Edge dialog to specify the rising edge of bit 7 (and all other bits as "don't cares").

#### To run the measurement

1. Select the Run Single button.

#### To display the captured data

1. From the Window menu, select your logic analyzer and choose the  ${\it Waveform}$  command.

See Also

"For More Information..." on page 24

### Example: State measurement on counter board

This example uses the demo counter board that is supplied with the *Making Basic Measurements* kit as the device under test. The kit is supplied with every logic analysis system, or can be ordered from your Agilent Technologies Sales Office.

#### To connect the logic analyzer to the device under test

Connect Pod 1 of the logic analyzer to J1 on the demo counter board.

The demo counter board has built-in terminations and header connectors.

#### To choose the sampling mode

- 1. In the Sampling tab, choose *State Mode*.

- 2. In the Clock Setup, using the *Master only* mode, specify the rising edge of the J clock as the sampling clock.

#### To format labels for the probed signals

- 1. In the Format tab, select the button under the pod 1.

- 2. In the Pod threshold dialog, select TTL; then, select the Close button.

- 3. Select a label button.

- 4. Choose the *Rename* command, enter the label name "SCOUNT", and select the OK button.

- 5. In the label row, select the button under pod 1.

- 6. Choose the ".......\*\*\*\*\*\*\* standard label assignment to assign the lower 8 bits of pod 1 to the "SCOUNT" label.

#### To define the trigger condition

- 1. In the Trigger tab, and in the Trigger Functions subtab, choose the "Find pattern n times" trigger function, and select the *Replace* button.

- 2. In the Trigger Sequence portion of the Trigger tab, enter "15" in the occurrence count field, and enter enter "FX" in the label value field.

#### To run the measurement

1. Select the Run Single button.

#### To display the captured data

1. From the Window menu, select your logic analyzer and choose the Listing command.

See Also

"For More Information..." on page 24

**Chapter 1: Getting Started**

**Example: State measurement on counter board**

## Task Guide

- "Probing the Device Under Test" on page 33

- "Choosing the Sampling Mode" on page 36

- "Selecting the Timing Mode (Asynchronous Sampling)" on page 36

- "Selecting the State Mode (Synchronous Sampling)" on page 43

- "In Either Timing Mode or State Mode" on page 52

- "Using 2 GHz Timing Zoom" on page 54

- "Formatting Labels for Logic Analyzer Probes" on page 57

- "Setting Up Triggers and Running Measurements" on page 64

- "Using Trigger Functions" on page 65

- "Using State Mode Trigger Features" on page 70

- "Editing the Trigger Sequence" on page 72

- "Editing Advanced Trigger Functions" on page 78

- "Saving/Recalling Trigger Setups" on page 85

- "Running Measurements" on page 86

- "Displaying Captured Data" on page 88

- "Using Symbols" on page 95

- "Printing/Exporting Captured Data" on page 104

- "Cross-Triggering" on page 106

- "Solving Logic Analysis Problems" on page 108

- "Saving and Loading Logic Analyzer Configurations" on page 110

Measurement Examples (see the *Measurement Examples* help volume)

See Also

### Probing the Device Under Test

The figures below shows a variety of simple probing connections. The specific probe type, number of probes, and location on the device under test circuit depends on your particular measurement.

For equivalent circuit diagrams and pinouts, see the description of the probe type in the *Logic Analysis System and Measurement Modules Installation Guide*. If you have misplaced the *Logic Analysis System and Measurement Modules Installation Guide*, you can download the latest version from the world-wide web at:

http://www.cos.agilent.com/manuals/logic analyzers.html#la 16700b

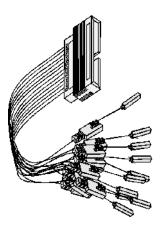

### Probe Lead-to-Board Connection

The standard lead set plugs directly into any .1-inch grid with 0.026 to 0.033-inch diameter round pins or 0.025-inch square pins. All probe tips work with the Agilent Technologies 5059-4356 surface mount grabbers and the Agilent Technologies 5959-0288 through-hole grabbers.

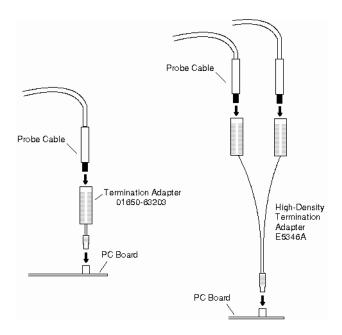

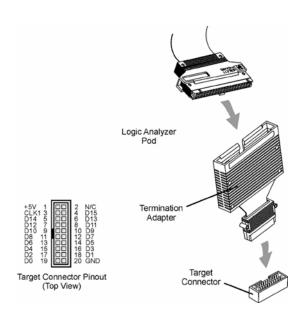

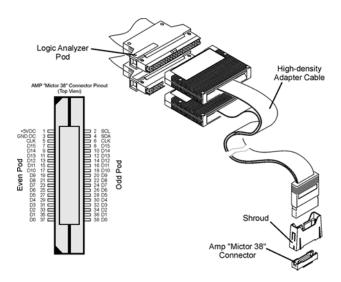

## Adapter-to-Board Connection

Both the 01650-63203 and the E5346A adapters include termination for the logic analyzer. The 01650-63203 termination adapter plugs into a 2 x 10 pin header with 0.1 inch spacing. The E5346A high-density adapter connects to an AMP "Mictor 38" connector. If possible, use support shrouds around the Mictor connector to relieve strain and improve connections.

## Direct Pod-to-Board Connection

If you provide proper termination as part of the device under test board, you can plug the pod directly into the ©3M 2520-series, or similar alternative connector. Suggested termination is shown in the Logic Analysis System and Measurement Modules Installation Guide.

Also use this termination with the Agilent Technologies E5351A high-density, non-terminated adapter.

#### Pod-to-Analysis Probe Connection

Analysis probes (formerly called preprocessors) are microprocessorspecific interfaces that make it easier to probe buses. Generally, analysis probes consist of a circuit board that attaches to the microprocessor (possibly through an adapter) and a configuration file. The configuration file sets up the logic analyzer's clocks and labels correctly, and may include an inverse assembler. The circuit board provides access to logical groups of pins through headers designed to connect directly to the logic analyzer.

The easiest way to set up a measurement with an analysis probe is the Setup Assistant (see the *Setup Assistant* help volume). The Setup Assistant asks you questions about your measurement and then shows you just the information you need to set up the probe correctly. It also loads the proper configuration files.

See Also

<u>http://www.agilent.com/find/Laaccessories/</u> for more information on Agilent logic analyzer probing accessories.

### Choosing the Sampling Mode

There are two logic analyzer sampling modes to choose from: *timing mode* and *state mode*.

In *timing mode*, the logic analyzer samples asynchronously, based on an internal sampling clock signal.

In *state mode*, the logic analyzer samples synchronously, based on a sampling clock signal (or signals) from the device under test. Typically, the signal used for sampling in state mode is a state machine or microprocessor clock signal.

- "Selecting the Timing Mode (Asynchronous Sampling)" on page 36

- "Selecting the State Mode (Synchronous Sampling)" on page 43

- "In Either Timing Mode or State Mode" on page 52

- "Using 2 GHz Timing Zoom" on page 54

# Selecting the Timing Mode (Asynchronous Sampling)

In *timing mode*, the logic analyzer samples asynchronously, based on an internal sampling clock signal.

- "To select the timing mode" on page 40

- "To select the full/half channel configuration" on page 41

- "To select transitional timing or store qualified" on page 37

- "To specify the sample period" on page 42

# To select transitional timing or store qualified

1. In the Sampling tab with Timing Mode selected, select the Transitional Timing with Store Qualification configuration.

## **Transitional Timing**

In Conventional Timing Acquisition mode, the analyzer stores measurement data at each sampling interval. In Transitional Timing Acquisition mode, the timing analyzer samples data at regular intervals, but only stores data when there is a threshold level transition. Each time a level transition occurs on any of the bits, data on all channels is stored. A time tag is stored with each stored data sample so the measurement can be reconstructed and displayed later.

#### NOTE:

Transitional timing or store qualified timing, requires time tags to recreate the data. Time tags are either stored in the memory resources of an unused pod pair, or they are interleaved with the data in memory. If tags are interleaved with the data, available memory depth is reduced by half.

## **Store Qualified Timing**

Store qualified timing allows you to specify what data is stored during the course of an acquisition. The level of data qualification can be simple (Store Anything or Store Nothing), or more complex (Custom).

For information on setting up store qualification, refer to To specify default storing (see page 71)

## See Also

"More on Storing Transitions" on page 38

"Transitional Timing Considerations" on page 39

"Default Storing Subtab" on page 156

# More on Store Qualification in Transitional Timing

When *Transitions* is selected on the *Default Storing* subtab, the default store qualification is setup to store data on all channels if an edge/transition occurs on any one channel. Only active channels (channels assigned to labels) are used. No further user action is required.

If certain channels have a high occurrence of transitions that are meaningless in the context of the measurement, they can be ignored with the following procedure.

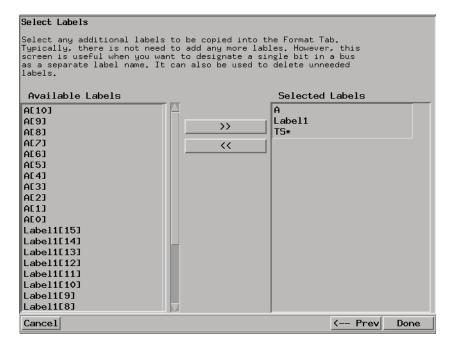

- 1. Select Select Labels.

- 2. From the *Transitions Label Select* dialog that appears, highlight the desired label from the *Available Labels* list, then select the right-arrow to move the selection to the *Ignore Edges On* list.

- 3. Repeat as needed for additional labels.

- 4. Select *OK* to save the selection and close the dialog. Selecting *Cancel*, will undo any changes and close the dialog.

Unlike the *Custom* default storing mode, when *Transitions* is selected, no other qualifier events like patterns, ranges, etc., are available. Also, storing cannot be enabled or disabled in the sequence branch action lists.

#### NOTE:

If you have a bit that is shared across multiple labels, all labels containing that bit must be on the Ignore list before transitions on that bit will no longer cause a sample to be stored.

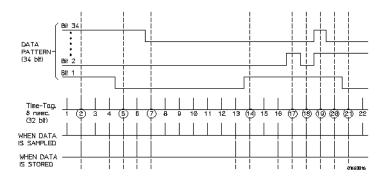

# More on Storing Transitions

#### **Minimum Transitions Stored**

Normally, transitions have not occurred at each sample period. This is illustrated below with time-tags 2, 5, 7, and 14. When transitions

happen at this rate, two samples are stored (four at the fastest rate of 2.5 ns) for every transition. Therefore, with 2 K samples of memory, 1 K of transitions are stored. You must subtract one, which is necessary for a starting point, for a minimum of 1023 stored transitions.

#### **Maximum Transitions Stored**

If transitions occur at a fast rate, such that there is a transition at each sample point, only one sample is stored for each transition as shown by time tags 17 through 21 below. If this continues for the entire trace, the number of transitions stored is 2 K samples. Again, you must subtract the starting point sample, which then yields a maximum of 2047 stored transitions.

In most cases a transitional timing trace is stored by a mixture of the minimum and maximum cases. Therefore, in this example the actual number of transitions stored will be between 1023 and 2047.

# **Transitional Timing Considerations**

## **Data Storage**

When an edge is detected, two samples (four when sampling at 2.5 ns) are stored across all channels assigned to the timing analyzer. The need of two samples is to avoid loss of data if a second edge were to occur to soon after the first edge for the edge detectors to reset.

## Sequence level branching

In transitional timing, only 2 branches are available per sequence level.

#### **Global counters**

In transitional timing, only one global counter is available.

## **Storing Time Tags**

Transitional timing requires time tags to recreate the data. Time tags are either stored in the memory resources of an unused pod pair, or they are interleaved with the data in memory. If tags are interleaved in data, available memory depth is reduced by half.

## **Increasing Duration of Storage**

Using the *Transitional Label Select* dialog to specify selected labels to ignore can increase usable memory depth and acquisition time by ignoring transitions on signals like clock or strobe that add little useful information to the measurement when no other signals are transitioning.

#### **Invalid Data**

The analyzer only looks for transitions on data lines on labels that are turned on. Data lines on labels that are turned off store data, but only when one of the lines that is turned on transitions. If the data line on a label is turned on after a run, or the data line is assigned to a new label, you would see data, but it is unlikely that every transition that occurred was captured.

## **Trigger Position**

In transitional timing, no data prestore (samples acquired before trigger) is required. Therefore, much like state mode, the trigger position (start/center/end) will indicate the percentage of memory filled with samples after the trigger. The number of samples acquired/displayed before trigger will vary between measurements.

# To select the timing mode

1. Open the logic analyzer Setup window.

- 2. Select the Sampling tab.

- 3. Choose the Timing Mode option.

You can also select the timing sampling mode in the "Pod Assignment Dialog" on page 130.

## To select the full/half channel configuration

- 1. In the Sampling tab, with Timing Mode selected, select the timing analyzer configuration. You can choose between:

- 2M Sample Full Channel 333 MHz

In this configuration, the total memory depth is 2M samples per *channel*, with data being sampled and stored as often as every 3.0 ns. You can set the sample rate to go slower with the Sample Period control.

#### NOTE:

When the Sample Period is 3.0 ns, data is acquired at two times the trigger sequencer rate. This means that data must be present for at least two samples before the trigger sequencer can reliably detect it. The trigger sequencer could miss data present for less than two sample periods.

The trigger sequencer treats the data as a group of two samples for each sequencer clock. This means that the trigger point indication could be off by one sample.

Although the trigger sequencer cannot detect all data, the analyzer will correctly capture all data present for at least one sample period.

4M Sample Half Channel 667 MHz

In this configuration, only one pod of each pod pair is available. Channels assigned to unavailable pods are ignored. You can specify which pod to use by toggling the Pod field in Format.

The total memory depth is 4M samples per *channel*. Data is sampled and stored every 1.5 ns; this rate cannot be changed.

## To select transitional timing or store qualified

#### NOTE:

When the Sample Period is 1.5 ns, data is acquired at four times the trigger sequencer rate. This, along with other half-channel mode characteristics, means that data must be present for at least five samples before the trigger sequencer can reliably detect it. The trigger sequencer cannot detect data present for less than two sample periods, and could miss data present for less than five sample periods.

The trigger sequencer treats the data as a group of four samples for each sequencer clock. This means that the trigger point indication could be off by up to three samples.

Although the trigger sequencer cannot detect all data, the analyzer will correctly capture all data present for at least one sample period.

2. If you chose the 667 MHz Half Channel 4M Sample configuration, select the Format tab and choose which pod of the pod pair will be used to sample data.

#### See Also

"To specify the sample period" on page 42

## To specify the sample period

When the logic analyzer is in timing (asynchronous sampling) mode, the *Sample Period* setting specifies how often the logic analyzer samples the signals from the device under test.

1. In the Sampling tab, with Timing Mode selected, enter the desired time between logic analyzer samples.

To capture signal level changes reliably, the sample period should be less than half (many engineers prefer one-fourth) of the period of the fastest signal you want to measure.

The sample rate is the inverse of the sample period.

#### NOTE:

In conventional timing mode the sample rate is fixed at 1.25 ns.

# Selecting the State Mode (Synchronous Sampling)

In *state mode*, the logic analyzer samples synchronously, based on a sampling clock signal (or signals) from the device under test. Typically, the signal used for sampling in state mode is a state machine or microprocessor clock signal.

- "To select the state mode" on page 44

- "To select the 167 MHz/333 MHz state speed configuration" on page 44

- "To change the sampling clock mode" on page 44

- "To set up the sampling clock" on page 46

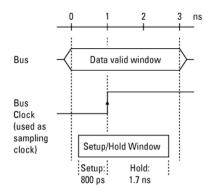

# State Mode Sampling Position

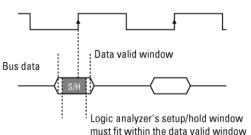

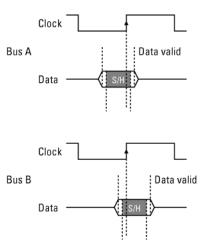

In order for a *state mode* logic analyzer to accurately capture data from a device under test, the logic analyzer's setup/hold time (window) must fit within the device under test's data valid window.

Because the location of the data valid window relative to the bus clock is different for different types of buses, the logic analyzer lets you adjust the sampling position in order to accurately capture data on high-speed buses (see "Understanding State Mode Sampling Positions" on page 208).

When the device under test's data valid window is less than 2.5 ns (roughly, for clock speeds >= 200 MHz), it's easiest to use *eye finder* to locate the stable and transitioning regions of signals and to automatically adjust sampling positions.

• "To automatically adjust sampling positions" on page 47

When the device under test's data valid window is greater than 2.5 ns (roughly, for clock speeds < 200 MHz), it's easiest to adjust the sampling position manually, without using the logic analyzer to locate the stable and transitioning regions of signals.

• "To manually adjust sampling positions" on page 50

## To select the state mode

- 1. Open the logic analyzer Setup window.

- 2. Select the Sampling tab.

- 3. Choose the State Mode option.

You can also select the state sampling mode in the "Pod Assignment Dialog" on page 130.

## To select the 167 MHz/333 MHz state speed configuration

- 1. In the Sampling tab, with State Mode selected, select the state analyzer configuration. You can choose between:

- 167 MHz / 2M State

In this configuration, all pods are available.

Memory depth is 2M samples per *channel*. If time or state *count* is turned on in *Trigger Settings*, the total memory is split between data acquisition storage and time or state count storage. To maintain the full memory depth of 2M samples per channel, leave one pod pair unassigned. (To unassign a pod pair, select the *Pod Assignment* button in the *Format* tab, then drag a pod pair to unassigned.)

State clock speed matches your device under test's clock, up to 167 MHz.

• 333 MHz / 2M State

This configuration is similar to the 167 MHz State mode, except clocking is restricted to the J clock on Pod 1 of the *master card* of the *module*, and triggering is restricted to two trigger functions.

NOTE:

When Store Qualification is performed in the 333 MHz State mode, there may be the case where data occupying memory is further disqualified. As a result, you may see a non-contiguous listing of states as well as a reduction of usable memory.

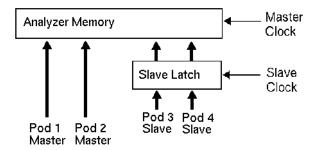

# To change the sampling clock mode

Normally, in the  $Master\ only\ sampling\ clock\ mode$ , there is one sampling clock signal. When a clock edge occurs, data is captured and

saved into one sample of logic analyzer memory.

Two additional sampling clock modes let you capture data differently:

• In the *Master/Slave* mode, you can save data captured on different clock edges into the same sample of logic analyzer memory.

When the slave clock occurs, data captured on the pods that use the slave clock is saved in a slave latch. Then, when the master clock occurs, data captured on the pods that use the master clock, as well as the slave latch data, are saved into logic analyzer memory.

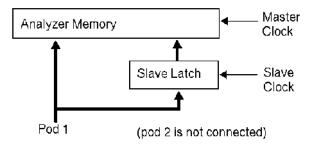

• In the *Demultiplex* mode, you can demultiplex data being probed by one pod into the logic analyzer memory that is normally used for two pods.

When the slave clock occurs, data captured on the pod is saved into the slave latch for the other pod in the *pod pair*. Then, when the master clock occurs, data captured on the pod, as well as the slave latch data, are saved in logic analyzer memory.

## To set up the master sampling clock mode

1. In the Sampling tab, with State Mode selected, select the *Master only* mode in the Clock Setup area.

## To set up the master/slave sampling clock mode

- 1. In the Sampling tab, with State Mode selected, select the *Master/Slave* mode in the Clock Setup area.

- 2. In the Format tab, select *Slave Clock* for each pod that should use the slave clock, and select *Master Clk* for each pod that should use the master clock.

## To set up the demultiplex sampling clock mode

- 1. In the Sampling tab, with State Mode selected, select the *Demultiplex* mode in the Clock Setup area.

- 2. In the Format tab, select *Demultiplex* for the pod pair that should use this mode.

## To set up the sampling clock

- 1. In the Sampling tab, with the State Mode selected, make sure the *Advanced Clocking* box is unchecked.

- 2. For each clock input signal that will be used:

- a. Select the pod's Master or Slave button (under the activity indicator).

- b. If the signal edge will specify when to sample, choose *Rising Edge*, *Falling Edge*, or *Both Edges*.

- c. If the signal level will enable the sampling clock, choose *Qualifier High* or *Qualifier Low*.

- 3. Make sure all unused clock inputs are turned Off.

## To set up using advanced clocking

- 1. In the Sampling tab, with the State Mode selected, select the *Advanced Clocking* check box.

- 2. Select the *Master Clock* button. In the Master clock dialog, select the appropriate options for setting up the master clock.

- 3. If you have chosen the Master/Slave or Demultiplex clock mode, select the *Slave Clock* button. In the Slave clock dialog, select the appropriate options for setting up the slave clock.

#### See Also

"To change the sampling clock mode" on page 44

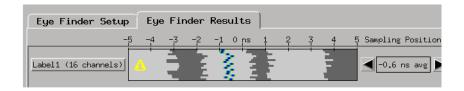

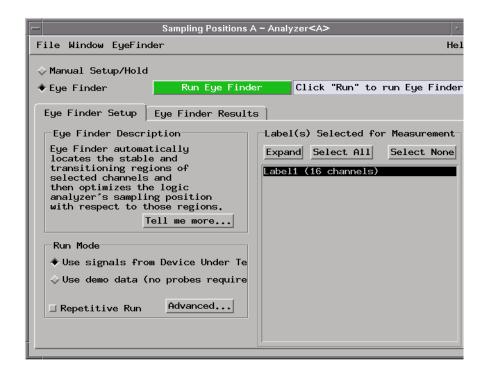

## To automatically adjust sampling positions

When adjusting the state mode sampling position with *eye finder*, the logic analyzer looks at signals from the device under test, figures out the location of the data valid window in relation to the sampling clock, and automatically sets the sampling position.

Because *eye finder* automatically runs on individual channels, it can correct for the small delay effects caused by probe cables and circuit board traces. This makes the logic analyzer's setup/hold window smaller and lets you accurately capture data at higher clock speeds.

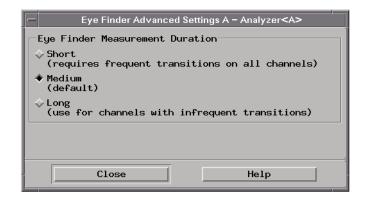

## Eye finder requires:

- At least 500 transitions on each signal during its run. (You can use the advanced *eye finder* settings to cause longer or shorter runs.)

- All devices which can drive each signal should contribute to the stimulus.

- All device under test operating modes relevant to the eventual logic analysis measurement should contribute to the stimulus as well.

## NOTE:

Eye finder measurements and normal logic analyzer measurements cannot run simultaneously.

## To run eye finder

- 1. Probe the device under test by connecting the logic analyzer channels.

- 2. Select the state (synchronous sampling) mode (see "To select the state mode" on page 44).

- 3. Format labels for those logic analyzer channels.

- 4. Make sure that the device under test and the logic analyzer have warmed up to their normal operating temperatures.

- 5. In the Format tab, select the Setup/Hold button.

- 6. In the Sampling Positions dialog, select the Eye Finder option.

- 7. In the Eye Finder Setup tab, select the *Use signals from Device Under Test* option.

## To select transitional timing or store qualified

The *Use demo data* (no probes required) option is for demonstration purposes only.

8. Choose the labels that you wish to run eye finder on.

You may want to run *eye finder* on channel subsets, for example, when certain bus signals transition in one operating mode (of the device under test) and other bus signals transition in a different operating mode.

9. Select the Run Eye Finder button.

For more information on run messages, see "Eye Finder Run Messages" on page 136.

When *eye finder* finds more than one stable region on a channel, it uses the current sampling position as a hint about which stable region it should suggest a position for.

If *eye finder* picks the wrong stable region, you can expand the label and drag the blue Sampling Position line into the correct stable region. The suggested sampling position for that region will be shown (see "How Selected/Suggested Positions Behave" on page 135).

10. If you have moved the sampling position and wish to return to the suggested positions, go to the Eye Finder Results tab, select a label button or the Results menu, and choose the "set to suggested" command.

For more information on informational messages in the Eye Finder Results tab, see "Eye Finder Info Messages" on page 139.

Eye finder finds optimal sampling positions for the actual specific conditions -- amplitude, offset, slew rates, and ambient temperature. Therefore, you will get the best results by running eye finder under the same conditions that will be present when logic analysis measurements are made.

## To run *eye finder* repetitively

- 1. Select the *Repetitive Run* option in the Eye Finder Setup tab.

- 2. Select the  $Run\ Eye\ Finder\ (r)$  button.

In the Eye Finder Results tab, you can see how the stable and transitioning areas vary over time.

3. Select the *Stop Eye Finder* button.

## To view eye finder data as a bus composite

When you want a compressed, high-level view of the *eye finder* data:

1. In the Eye Finder Results tab, select the label button and choose the *View* as Bus Composite command.

Average sampling positions as well as stable and transitioning areas are displayed for the whole label. This is the default. Stable areas show positions where every channel in the label is stable.

#### To view eye finder data as a stack of channels

When you want more resolution in your view of the *eye finder* data:

1. In the Eye Finder Results tab, select the label button and choose the *View* as *Stack of Channels* command.

Individual sampling positions and stable and transitioning areas for all the channels in a label are shown.

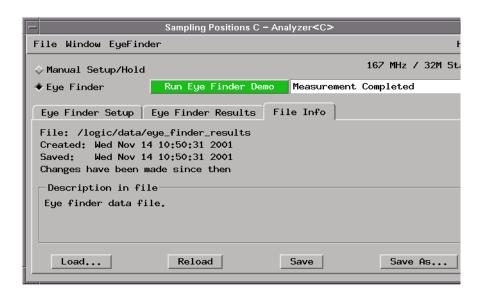

## To save/load eye finder data

While the *eye finder* sampling positions are saved with the logic analyzer configuration, *eye finder* measurement data is not; therefore, *eye finder* data must be saved and loaded separately.

1. In the File Info tab, select the Save As... or Load... buttons.

You can also choose the *Save Eye Finder* or *Load Eye Finder* command from the File menu.

## To select transitional timing or store qualified

2. In the file browser dialog, name the file to be saved or select the file to be loaded

For more information on save/load messages, see "Eye Finder Load/Save Messages" on page 141.

See Also

"Understanding State Mode Sampling Positions" on page 208

"Eye Finder Advanced Settings Dialog" on page 133

"To manually adjust sampling positions" on page 50

# To manually adjust sampling positions

## To use the Eye Finder option

Although the *Eye Finder* option was intended for automatically adjusting state mode sampling positions, you can also use it to manually adjust sampling positions. You don't have to *Run Eye Finder* to locate stable and transitioning regions on signals, just go directly to the Eye Finder Results tab, and drag the sampling positions to the proper locations.

- 1. Select the state (synchronous sampling) mode (see "To select the state mode" on page 44).

- 2. In the Format tab, select the Setup/Hold button.

- 3. In the Sampling Positions dialog, select the Eye Finder option.

- 4. In the Eye Finder Results tab, drag the sampling positions to the proper locations.

You can select bus labels to expand or collapse the channels in the label.

When using the Eye Finder option to manually adjust state mode sampling positions, the sampling positions are saved with the logic analyzer configuration (see "Saving and Loading Logic Analyzer Configurations" on page 110).

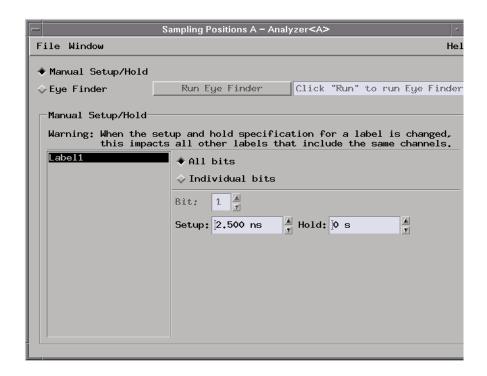

## To use the Manual Setup/Hold option

When adjusting the state mode sampling position with the *Manual Setup/Hold* option, you adjust the logic analyzer's setup/hold window relative to the sampling clock signal from the device under test. The

setup time is the front edge of the setup/hold window relative to the sampling clock, and the hold time is the back edge of the setup/hold window relative to the sampling clock.

- 1. Select the state (synchronous sampling) mode (see "To select the state mode" on page 44).

- 2. In the Format tab, select the Setup/Hold button.

- 3. In the Sampling Positions dialog, select the Manual Setup/Hold option.

- 4. For each label, enter setup/hold values. The values are adjustable in 100 ps increments, with a fixed window of 2.5 ns.

- 5. If you need to adjust bits individually:

- a. Select a label containing the bit.

If a bit is used in more than one label, you will change its setup and hold value in *all* labels.

- b. Select the *Individual bits* option.

- c. Enter the bit number you want to change.

- d. Enter the setup/hold value.

- 6. Close the Sampling Positions dialog.

The Manual Setup/Hold sampling positions are saved and loaded along with the logic analyzer configuration file.

## **Example**

Suppose you're probing a bus in the device under test whose data valid window is 3 ns. Suppose also that the bus clock edge occurs 1 ns into the data valid window. To place the logic analyzer's setup/hold window within the data valid window, you could specify a setup value of 800 ps (and hold value of 1.7 ns).

## To select transitional timing or store qualified

(The actual sampling position is in the middle of the setup/hold window.)

#### See Also

"Understanding State Mode Sampling Positions" on page 208

"To automatically adjust sampling positions" on page 47

# In Either Timing Mode or State Mode

- "To specify the trigger position" on page 52

- "To set acquisition memory depth" on page 53

- "To name an analyzer" on page 53

- "To turn an analyzer off or on" on page 53

# To specify the trigger position

1. In the Sampling tab (or in the Settings subtab of the Trigger tab), select the trigger position.

Specify whether you want to look at data after the trigger (Start), before and after the trigger (Center), before the trigger (End), or use a percentage of the logic analyzer's memory for data after the trigger (User Defined).

In Conventional Timing Mode, when a Run is started, the analyzer will

not look for a trigger until the specified percentage of pretrigger data has been stored. After a trigger has been detected, the specified percentage of posttrigger data is stored before the analyzer halts.

In State and Transitional Store Qualified modes, when a Run is started, the analyzer immediately looks for the trigger condition. In other words, the trigger position setting specifies the *maximum* amount of data that should be stored before the trigger.

## To set acquisition memory depth

If you need less data and want measurements to run faster, you can limit the number of samples that are stored in logic analyzer acquisition memory.

1. In the Sampling tab (or in the Settings subtab of the Trigger tab), select the acquisition depth.

The number of samples that can be chosen for the Acquisition Depth are approximations. The combination of *count* tags, pod assignments, and configuration modes affect what choices are available.

## To name an analyzer

You can give more descriptive names to a logic analyzer.

- 1. In the Sampling tab, select the  $Analyzer\ Name$  field.

- 2. Enter the new name.

The name now appears below the instrument tool icon in the workspace.

You can also name analyzers in the "Pod Assignment Dialog" on page 130.

# To turn an analyzer off or on

You may want to turn an analyzer off if you don't want it to be included in further measurements.

## To turn an analyzer off

1. In the Sampling tab, select the On box that is checked.

## To select transitional timing or store qualified

- 2. In the Analyzer Shutdown Options dialog, choose either:

- Soft -- This will leave the logic analyzer window but turn off most options.

- Hard -- This will remove the logic analyzer and its display tools from the Workspace.

You can also turn an analyzer off in the "Pod Assignment Dialog" on page 130.

## To turn an analyzer back on

- 1. If you used the *Soft* option when turning the logic analyzer off, you can turn it on again by selecting the *Off* check box.

- 2. If you used the *Hard* option when turning the logic analyzer off, you can turn it on again by selecting the *Setup* button in the System window or by dragging the analyzer's instrument tool icon to the workspace in the Workspace window.

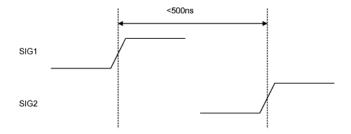

# Using 2 GHz Timing Zoom

Timing Zoom collects additional high-speed timing data around the trigger of the logic analyzer. It uses a 16K-sample, 2 GHz timing analyzer to sample data as closely as every 500 ps on all channels.

The Timing Zoom settings are accessed through the Timing Zoom button under *Sampling*.

- "To turn Timing Zoom on or off" on page 54

- "To set the Timing Zoom trigger position" on page 55

- "To specify which analyzer has Timing Zoom" on page 56

- "To set the Timing Zoom sample period" on page 56

# To turn Timing Zoom on or off

If you are not interested in the Timing Zoom data for a measurement, you can turn off Timing Zoom and improve logic analyzer performance.

- 1. In the Sampling tab, select the Timing Zoom button.

- 2. In the Timing Zoom controls dialog, select the On/Off checkbox.

## To set the Timing Zoom trigger position

- 1. In the Sampling tab, select the Timing Zoom button.

- 2. In the Timing Zoom controls dialog, select the trigger position.

Specify whether you want to look at Timing Zoom data after the trigger (Start), before and after the trigger (Center), before the trigger (End), or use a percentage of the logic analyzer's memory for data after the trigger (User Defined).

#### NOTE:

When in 333 MHz State mode (16717,18,19), the 400 MHz State mode (16750,51,52), or the 600 MHz State mode (16753, 54, 55, 56), the start of Timing Zoom data may occur after the actual trigger point. The reason for this data mis-alignment is due to how the trigger sequencer functions when in this mode.

The analyzer sequencer works on *Pairs* of samples. It will not evaluate the first sample of the pair until the second sample has entered the sequencer. If for example the trigger point is determined to be on the first sample, the analyzer displays the Timing Zoom data relative to the evaluation of the second sample. What ever time difference is seen between the two samples (of the pair) is reflected in the data display between the trigger point and the start of the Timing Zoom data.

This time difference can be noticeable if your measurement is using bursted clocks and the first sample (actual trigger point) is clocked on the last clock signal of a burst, and the second sample (of the pair) is clocked with the first clock of the next burst. The time difference between the clock bursts is reflected as a mis-alignment between the trigger point and the start of the Timing Zoom data.

The best thing to do to help mitigate this situation is to set the Timing Zoom to "Trigger Position End" to capture as much data near the first sample as possible.

## To specify which analyzer has Timing Zoom

## NOTE:

If you have both analyzers of the *module* turned on, you need to specify which analyzer you want to use Timing Zoom with.

- 1. In the Sampling tab, select the Timing Zoom button.

- 2. In the Timing Zoom controls dialog, select the analyzer that Timing Zoom will work with.

# To set the Timing Zoom sample period

If you want to see more or less sampling resolution around the trigger, you can adjust the Timing Zoom sample period.

- 1. In the Sampling tab, select the Timing Zoom button.

- 2. In the Timing Zoom controls dialog, select the sample period.

# Formatting Labels for Logic Analyzer Probes

The Format tab is mainly for assigning bus and signal names (from the device under test) to logic analyzer channels. These names are called labels. Labels are used when setting up triggers and displaying captured data.

The Format tab also lets you do things like assign pod pairs to one or two logic analyzers, specify the logic analyzer threshold voltage, change the label polarity, reorder bits in a label, and turn labels off or on.

The Format tab has activity indicators that show signal levels.

- "To assign pods to one or two analyzers" on page 57

- "To set pod threshold voltages" on page 58

- "To assign probe channels to labels" on page 59

- "To change the label polarity" on page 61

- "To reorder bits in a label" on page 61

- "To turn labels off or on" on page 62

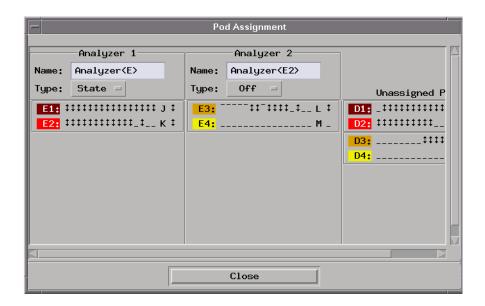

# To assign pods to one or two analyzers

A logic analyzer's pod pairs can be assigned to one or two separate logic analyzers or they can be left unassigned.

- 1. In the Format tab, select the Pod Assignment button.

- 2. In the Pod Assignment dialog, drag a pod pair to the appropriate logic analyzer.

- 3. Select the Close button.

When all pods are assigned and state or time counts are saved with the captured data, logic analyzer acquisition memory is halved to 1M samples.

## **Formatting Labels for Logic Analyzer Probes**

When using a multi-card logic analyzer:

- When both analyzers are turned on, pods 1/2 and 3/4 of the master card cannot be assigned to the same analyzer.

- Each *pod pair* has two *clock channels*, but only the clock channels of pods on the *master card* can be used in the analyzer's clocking setup. (The master card's pods needn't be assigned in order to use their clock channels).

## To turn on an analyzer that is off

1. Select Off and choose State or Timing.

(Only one analyzer at a time can be set to *Timing*.)

A second analyzer window appears after a pause for setup.

You can also turn on an analyzer that is off by opening the Workspace window and dragging the instrument tool icon onto the workspace.

See Also

"Pod Assignment Dialog" on page 130

# To set pod threshold voltages

The *threshold voltage* is the voltage level that a signal must cross before the logic analyzer recognizes a change in logic levels. In addition to a user defined choice, you can also select a predefined level from the standard choices.

## **Standard**

- 1. In the *Format* tab, select the threshold button located just below the pod name.

- 2. In the Pod threshold dialog, choose one of the standard threshold options:

- TTL -- The threshold level is +1.50 volts.

- LVTTL -- The threshold level is +1.40 volts.

- SSTL2 -- The threshold level is +1.50 volts.

- SSTL3 -- The threshold level is +1.25 volts.

- LVCMOS 1.5v -- The threshold level is +0.75 volts.

- LVCMOS 1.8v -- The threshold level is +0.90 volts.

- LVCMOS 2.5v -- The threshold level is +1.25 volts.

- LVCMOS 3.3v -- The threshold level is +1.65 volts.

- CMOS 5.0v -- The threshold level is +2.50 volts.

- ECL -- The threshold level is -1.3 volts.

- LVPECL -- The threshold level is 2.00 volts.

- 3. If you don't want the change to apply to all pods, deselect the checked box next to *Apply settings to all pods*.

- 4. Select the *Close* button.

#### **User Defined**

When *User Defined* is selected, the threshold level is selectable from - 6.0 volts to +6.0 volts.

#### NOTE:

The logic analyzer requires a minimum voltage swing of 500 mV at the probe tip to recognize changes in logic levels.

#### NOTE:

The threshold voltage specified also applies to the pod's clock input.

# To assign probe channels to labels

The logic analyzer lets you assign names (labels) to logic analyzer channels so that it's easier to set up triggers and interpret the captured data when displayed.

Typically, you give labels the names of the buses and signals in the device under test that are are being probed.

- 1. In the Format tab, select a label button, and either:

- Choose the *Rename* command, enter the label name, and select the OK button.

## **Formatting Labels for Logic Analyzer Probes**

- Or, choose the *Insert before* or *Insert after* command, enter the label name, and select the OK button.

- 2. In the label row, select the button of the pod that contains the channels you want to assign.

- 3. Either choose one of the standard label assignments or choose *Individual*.

- (\*) (asterisk) indicates an assigned bit.

- (.) (period) indicates an unassigned bit.

- (R) indicates an assigned bit in a reordered label.

If you chose *Individual*:

- a. In the "label pod" dialog, select the channels you want to assign/unassign.

- b. Select the OK button.

A maximum of 32 channels can be assigned to a label.

In the Format tab, least significant pod channels (bit 0) are on the right and most significant pod channels (bit 15) are on the left. (The bit numbers are shown just below the activity indicators.)

Labels can contain bits that are not consecutive; however, bits are always numbered consecutively within a label.

A label can include data and clock channels from more than one pod, but this places restrictions on the complexity of the trigger later.

#### To delete labels

- 1. Select the label name that you want to delete.

- 2. Choose Delete.

If only one label is defined, it cannot be deleted.

When you delete labels, their bit assignments are not saved. However, you can make a label inactive and save its bit assignments by turning the label off.

See Also

"To reorder bits in a label" on page 61

"To turn labels off or on" on page 62

"To change the label polarity" on page 61

# To change the label polarity

While negative logic is rare in circuits (the main exception at this time is RAMBUS), you can change the label polarity if the device under test uses negative logic.

1. In the Format tab, select the polarity button (next to the label button) to toggle between positive (+) and negative (-) polarity.

Positive polarity means that a high voltage is a logic "1".

Negative polarity means that a high voltage is a logic "0".

Changing the label polarity will have the following effects:

- "1" and "0" values flip in the trigger condition.

- Waveforms and bus values (where shown) invert in the Waveform display tool.

- "1" and "0" values flip in the Listing display tool.

Changing the label polarity does not affect:

- Edge definitions for clock setup and *edge terms*.

- Symbol definitions for the logic analyzer.

- Activity indicators.

# To reorder bits in a label

In cases where buses in the device under test haven't been probed with consecutive logic analyzer channels, you can reorder the bits in a label.

- 1. In the Format tab, select the label button whose bits you want to reorder.

- 2. Choose Reorder bits.

## **Formatting Labels for Logic Analyzer Probes**

- 3. In the Change Bit Order dialog:

- To reorder the bits individually, enter the bit that the probe channel should be mapped to.

- To swap the high and low order bytes or words, select the button *Big Endian to Little Endian* at the bottom of the dialog.

- To return to sequentially ordered bits, select the button *Default Order* at the bottom of the dialog.

- 4. Select the *OK* button.

The label now shows an "R" to indicate that the assigned bit has been reordered.

NOTE:

Labels with reordered bits cannot be used as  $range\ terms$  or <, <=,>, >= in triggers.

## To turn labels off or on

When you temporarily want to remove a label and its data, you can turn off the label. The label name and its bit assignments are preserved.

## To turn a label off

- 1. In the Format tab, select the label button that you want to turn off.

- 2. Choose Label [ON] to toggle it off.

At least one label must remain on.

#### To turn a label on

- 1. In the Format tab, select the label button that you want to turn on.

- 2. Choose *Label [OFF]* to toggle it on.

## To display a label that was off

- 1. Turn on the label.

- 2. At the bottom of the window, select the *Apply* button.

The label's data appears in the display windows.

# Setting Up Triggers and Running Measurements

The following information is a generic discussion about triggering in logic analyzers. Depending on the logic analyzer type, and the state or timing mode being used, some functionality may not be available.

- "Using Trigger Functions" on page 65

- "Using State Mode Trigger Features" on page 70

- "Editing the Trigger Sequence" on page 72

- "Editing Advanced Trigger Functions" on page 78

- "Saving/Recalling Trigger Setups" on page 85

- "Running Measurements" on page 86

#### In General...

Use trigger functions for basic measurements.

For more complicated measurements, where no trigger function exists, start with a trigger function that's similar to the measurement you want to make. Then, break down the trigger function and edit the advanced trigger sequence levels.

## Timing Analyzer Triggers

Everything that looks like a button in the trigger definition gives you a way to modify the trigger setup.

For example, to look for a edge instead of a pattern, select the button that equates a label with a pattern and choose an edge comparison instead.

## State Analyzer Triggers

For every state analysis sample, a logic analyzer needs to know two things:

- 1. Should some action (like a trigger) be taken as a result of this sample?

- 2. What should be done with this sample? That is, should it be stored in logic analyzer memory or should it be discarded? (This question doesn't need to be asked when using a timing analyzer because all samples are stored.)

State analysis trigger definitions are made simpler with a *default* storage qualifier. This makes it possible to ignore, at all trigger

sequence levels, the question about what to do with the captured data samples.

Of course, sometimes it's useful to specify storage qualifiers at certain levels in the trigger sequence. For this, you can insert storage *actions* in the trigger sequence before trigger or goto actions. Storage actions in the trigger sequence override the default storage qualifier for the samples that cause the trigger or goto actions to occur. Storage actions can also be used to turn on or off the default storing.

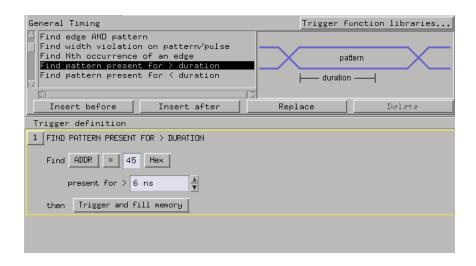

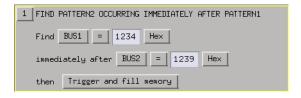

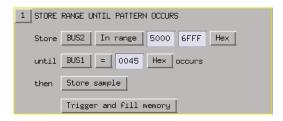

# **Using Trigger Functions**

Many common measurement setups are provided with the logic analyzer. These setups are called *trigger functions*, and you can use them for quick measurement setup.

For more complicated measurements, where no trigger function exists, start with a trigger function that's similar to the measurement you want to make. Then, *break down* the trigger function and edit the advanced trigger specification.

- "To select a trigger function" on page 65

- "To specify a label pattern event" on page 66

- "To specify a label edge event" on page 66

- "To break down a trigger function" on page 67

- "To create a trigger function library" on page 68

# To select a trigger function

- 1. In the Trigger tab's Trigger Functions subtab, select the appropriate trigger function.

- A picture describing the trigger function is shown.

- 2. Select the *Replace* button (or *Insert before* or *Insert after* button) to move it to the Trigger Sequence below.

- 3. In the Trigger Sequence, select and/or enter the appropriate labels, values,

and options.

## To specify a label pattern event

Label pattern events let you specify patterns or ranges on a bus.

1. Select the label name button and choose the label that you want to look for a pattern on.

You can also insert other label events if you want to look for multiple patterns on multiple labels. Once another label event is inserted, you can choose And if both label events must occur in the same sample or Or if only one of the label events must occur.

2. Select the operator button and choose the appropriate operator.

The *In range* and *Not in range* operators consider the values you enter to be inside the range. Ranges cannot be set on labels whose bits have been reordered.

3. Select the number base button, and choose the number base that you want.

If the number base is changed in one window, the number base in other windows may not change accordingly. For example, the number base assigned to symbols is unique, as is the number base assigned in the Listing window.

4. Enter the label value.

Xs mean you don't care about the value on the specified bits. Xs are not allowed in ranges.

If you chose the *Symbols* or *Line* #s number base, select the *Absolute XXXX* button, and use the Symbol Selector dialog to choose the symbol or line number value.

See Also

"To specify a label edge event" on page 66

"To enter symbolic label values" on page 99

"Symbols Selector Dialog" on page 161

# To specify a label edge event

Label edge events let you specify edges and glitches on a bus. Label

edge events are only available in certain timing mode trigger functions.

1. Select the label name button and choose the label that you want to look for a pattern on.

You can also insert other label events if you want to look for multiple patterns on multiple labels. Once another label event is inserted, you can choose And if both label events must occur in the same sample or Or if only one of the label events must occur.

- 2. Select the edge assignment button.

- 3. In the Specify Edge/Glitch dialog, select the edges or glitches that you're looking for on particular logic analyzer channels.

When you select multiple edges or glitches, they are ORed together, and any one of the edges or glitches in a sample will satisfy the label edge event. If you want to AND edges or glitches on a label, insert multiple label edge events and AND them together.

4. Select the OK button.

#### See Also

"To specify a label pattern event" on page 66

# To break down a trigger function

When a trigger function doesn't quite let you set up the trigger you want, you can break it down and edit the resulting advanced trigger function.

- 1. In the Trigger tab, select the number button of the trigger sequence level whose trigger function you want to break down.

- 2. Choose Break down function.

Breaking down the trigger function will be permanent (although you can choose the Undo command from the Edit menu if no other editing has taken place).

If you only want to look the advanced trigger function, without editing it, you can *expand* the trigger function.

3. Select OK in the confirmation dialog.

## **Setting Up Triggers and Running Measurements**

## To expand a trigger function

- 1. In the Trigger tab, select the number button of the trigger sequence level whose trigger function you want to expand.

- 2. Choose Expand function.

## To compress a trigger function

Expanded trigger functions can be compressed back into their original form.

- 1. In the Trigger tab, select the number button of the trigger sequence level whose trigger function you want to compress.

- 2. Choose Compress function.

See Also

"Editing Advanced Trigger Functions" on page 78 for information on editing trigger functions that are broken down.

## To create a trigger function library

You can create your own libraries of trigger functions that are separate from logic analyzer configuration files (unlike saved/recalled trigger setups).

- 1. In the Trigger tab's Trigger Functions subtab, select the *Trigger function libraries* button.

- 2. In the Trigger function libraries dialog, select the *Create* button.

- 3. In the Create User Library dialog, enter the library name and description, and select OK.

- 4. In the Edit Trigger Function Library dialog, choose the *Add function* button.

- 5. In the Create User Function dialog, enter the function name and description, and select the levels from the current trigger sequence that be the trigger function; then, select OK.

Once you have created a trigger function library with trigger functions, you can:

• Load or unload the trigger function library.

- Insert and break down trigger functions from the loaded library just like normal trigger functions.

- Copy trigger function libraries to other logic analysis systems and load them into other logic analyzers that have trigger function library capability.

- Edit the trigger function library, adding or deleting functions, or delete the library.

#### NOTE:

If a *trigger sequence* or configuration file uses a trigger function library that has been deleted, or a trigger function that has been deleted from a library, the logic analyzer replaces the missing function with the default trigger function.

## To load/unload trigger function libraries

- 1. In the Trigger tab's Trigger Functions subtab, select the *Trigger function libraries* button.

- 2. Select the library from the list.

Only libraries created in the same sampling mode are available.

3. Select the *Load* (or *Unload*) button.

All of the library's trigger functions are added to (or removed from) the list of trigger functions.

#### To copy trigger function libraries between systems

- 1. Connect your logic analysis system to the network. (see the *Agilent Technologies 16700A/B-Series Logic Analysis System* help volume)

- 2. Using a computer on your network, copy the appropriate files from the / logic/trigger\_functions/ directory to a central location, or directly to other logic analyzers on the network.

#### See Also

"To break down a trigger function" on page 67

"Saving/Recalling Trigger Setups" on page 85

# Using State Mode Trigger Features

When the logic analyzer sampling mode is *state*, you can specify whether a state or time count is stored with samples and you can set up the default storing options.

- "To count states or time" on page 70

- "To Specify Default Storing" on page 71

- "To specify whether default storing is initially on or off" on page 72

## To count states or time

When the logic analyzer sampling mode is *state*, you can specify whether a state or time count is stored with samples.

- 1. In the Trigger tab's Settings subtab, select the Count option button and choose either *Off*, *Time*, or *States*.

- 2. If you chose States:

- a. Select the *Define* button.

- b. In the State count qualify dialog, select the  $Count\ if\ or\ Count\ if\ NOT$  option.

- c. Specify events that identify the states to be counted or not counted.

- d. If you would like to specify the evaluation order of the event list, select *Group events*. Then, in the Group Events dialog, either select the *Add parens* button to group events or select the *Remove parens* button to ungroup events. When you're done grouping events, select the OK button.

When time or state counts are turned on and all pods are assigned, logic analyzer acquisition memory is halved to 1M samples for the 16717A logic analyzer. Leaving one *pod pair* unassigned gives you full memory depth.

See Also

"To assign pods to one or two analyzers" on page 57

## To Specify Default Storing

You can set up default storing so that only the data samples you're interested in are saved in logic analyzer acquisition memory.

#### NOTE:

Default storing in both state and timing modes require time tags to reconstruct the data. These time tags will be stored either in the memory resources of an unused pod pair, or interleaved in the data.

1. In the Trigger tab's Default Storing subtab, select the *store by default* option button and choose either *Anything*, *Nothing*, *Custom*, or *Transitions*.

Anything means all samples are stored. Nothing means that no samples are stored. Custom lets you specify which samples are stored. Transitions lets you specify which transitions to store on a per label basis.

- 2. If you chose *Custom*:

- a. Select the Store if or Store if NOT option.

- b. Specify events that identify the states to be stored or not stored.

- c. If you would like to specify the evaluation order of the event list, select *Group events*. Then, in the Group Events dialog, either select the *Add parens* button to group events or select the *Remove parens* button to ungroup events. When you're done grouping events, select the OK button.

- 3. If you chose *Transitions* (Timing mode only).

Transitional timing is a subset of store qualified timing. In transitional timing, the store qualification is set to look for edges (transitions) on all active channels. Active channels are those that have been assigned to a label in the Format tab. Samples are stored for all channels whenever a transition occurs. No other store qualification events are allowed.

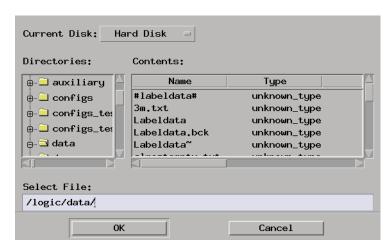

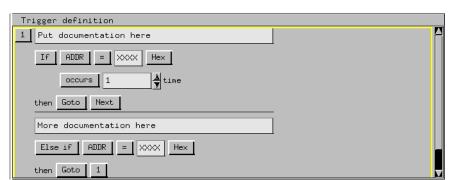

For more information on store qualification in transitional timing mode, refer to More on Store Qualification in Transitional Timing. (see page 38)